## (19)日本国特許庁(JP)

識別記号

(51) Int.Cl.7

## (12) 公開特許公報(A)

FΙ

(11)特許出願公開番号 特開2000-258892 (P2000-258892A)

テーマコード(参考)

(43)公開日 平成12年9月22日(2000.9.22)

|                       |                | • • •                                                                                                                                    |                                                                                                                                                                                                                                                                                   |

|-----------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8                     | G03F 1/08      | A 2H                                                                                                                                     | 095                                                                                                                                                                                                                                                                               |

| 8                     | H01L 21/28     | D 4 M                                                                                                                                    | 104                                                                                                                                                                                                                                                                               |

| 27                    | 21/30          | 502P 5F                                                                                                                                  | 064                                                                                                                                                                                                                                                                               |

| 2                     | 21/82          | D                                                                                                                                        |                                                                                                                                                                                                                                                                                   |

|                       |                | С                                                                                                                                        |                                                                                                                                                                                                                                                                                   |

|                       | 審查請求 未請求       | : 請求項の数7 OL (                                                                                                                            | 全 15 頁)                                                                                                                                                                                                                                                                           |

| 特願平11-65639           | (71)出顧人 000003 | 078                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

|                       | 株式会            | 社東芝                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

| 平成11年3月11日(1999.3.11) | 神奈川            | 県川崎市幸区堀川町72番地                                                                                                                            | b                                                                                                                                                                                                                                                                                 |

|                       | (72)発明者 金井     | 秀樹                                                                                                                                       |                                                                                                                                                                                                                                                                                   |

|                       | 神奈川            | 県川崎市幸区小向東芝町 1                                                                                                                            | 株式会                                                                                                                                                                                                                                                                               |

|                       | 社東芝            | 研究開発センター内                                                                                                                                |                                                                                                                                                                                                                                                                                   |

|                       | (74)代理人 100083 | 806                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

|                       | 弁理士            | 三好 秀和 (外7名)                                                                                                                              |                                                                                                                                                                                                                                                                                   |

|                       | Fターム(参考) 2H    | 095 BB01 BB03                                                                                                                            | •                                                                                                                                                                                                                                                                                 |

|                       | 41/            | 104 AA01 BB01 CC05 DD16                                                                                                                  | DD62                                                                                                                                                                                                                                                                              |

|                       |                | EE03 GG14 HH14                                                                                                                           |                                                                                                                                                                                                                                                                                   |

|                       | 5F             | 064 BB09 BB13 DD08 DD14                                                                                                                  | DD24                                                                                                                                                                                                                                                                              |

|                       | 1              |                                                                                                                                          |                                                                                                                                                                                                                                                                                   |

|                       |                | 8 H01L 21/28 21/30 21/82 審査請求 未請求 特願平11-65639 (71)出願人 000003 株式会 平成11年3月11日(1999.3.11) (72)発明者 金井 神奈川 社東芝 (74)代理人 100083 弁理士 Fターム(参考) 2H | ### HO1L 21/28 D 4M 27 21/30 502P 5F 2 21/82 D C 審査請求 未請求 請求項の数7 OL ( 特願平11-65639 (71)出願人 000003078 株式会社東芝 平成11年3月11日(1999.3.11) 神奈川県川崎市幸区堀川町72番頃 (72)発明者 金井 秀樹 神奈川県川崎市幸区小向東芝町1 社東芝研究開発センター内 (74)代理人 100083806 井理士 三好 秀和 (外7名) Fターム(参考) 2H095 BB01 BB03 4M104 AA01 BB01 CC05 DD16 |

## (54) 【発明の名称】 マスクパターン設計方法

## (57) 【要約】

·【課題】 アラインメント誤差による連結配線部の寸法変動を無くすこと及び、ゲート部の制御性を向上させること。

・【解決手段】 微細ゲート部と連結配線が近接する領域では、連結配線を予め設定した基準値以上に遠ざける・(ステップ $106\sim108$ )ことにより、アラインメント誤差による連結配線部の寸法変動を無くすことができる。又、ゲート部を挟む開口の幅に応じて第100PCで補正を加え、更に、最も外側の開口の幅を内側の開口の幅に揃えるように第200PCで補正を加える(ステップ114)ことにより、ゲート部の制御性を向上させることができる。

1

#### ・【特許請求の範囲】

・【請求項1】 素子領域と配線のパターンデータを用い て論理演算を行うことにより複数のパターンデータを発 生させることによりマスクパターンを設計するマスクパ ターン設計方法において、

前記素子領域に予め設定した距離以下に近接する配線の 一部又は全部を前記設定距離以上になるように遠ざける 処理を含むことを特徴とするマスクパターン設計方法。 ・【請求項2】 前記遠ざける処理を施した配線の一部又 は全部に前記設定距離以下に近接するデバイスの構成要 素があるかどうかを検出し、

検出された場合は遠ざける処理を施した前記配線の一部 又は全部から該当のデバイスの構成要素を前記設定距離 以上遠ざける処理を行い、

その後、前記遠ざける処理を施したデバイスの構成要素 に前記設定距離以下に近接するデバイスの他の構成要素 があるかどうかを検出し、検出された場合は該当のデバ イスの構成要素を先に遠ざけたデバイスの構成要素から 前記設定距離以上遠ざける処理を行うことを、前記設定 距離以下に他のデバイスの構成要素が検出されなくなる まで、繰り返し行う処理を含むことを特徴とする請求項 1 記載のマスクパターン設計方法。

・【請求項3】 前記素子領域に配線の一部又は全部が前 記設定距離以下近づいている場合にこれを遠ざける処理

前記素子領域いずれかの領域に近接する線分を求め、 該線分上に位置する図形の角のポイントを含み該近接す る線分から予め設定した距離以下に位置する図形の角の ポイントを抽出し、

これを近接する方向に平行に移動させるアルゴリズムに より行うことを特徴とする請求項1又は2記載のマスク パターン設計方法。

・【請求項4】 素子領域と配線のパターンデータを用い て論理演算を行うことにより複数のパターンデータを発 生させることによりマスクパターンを設計するマスクパ ターン設計方法において、

予め設定した距離以下に素子領域と配線の一部又は全部 が近づいている場合には、該配線の少なくとも一部に対 に近接している開口を拡張するか、該配線に近接して新 たな開口を設けるパターンデータを発生させる処理を含 40 むことを特徴とするマスクパターン設計方法。

・【請求項5】 前記設定距離以下に素子領域と配線の一 部又は全部が近づいている場合には、該配線の少なくと も一部に近接している開口を拡張するか、該配線に近接 して新たな開口をレベンソンマスクとして形成するパタ ーンデータを発生させる処理を含むことを特徴とする請 求項4記載のマスクパターン設計方法。

・【請求項6】 素子領域と配線のパターンデータを用い て論理演算を行うことによりレベンソンマスクとして複

マスクの連続して位置する複数の開口部に対して、各開 口部の幅に応じて補正を加えてマスクパターンを設計す るマスクパターン設計方法において、

前記開口部の最も外側の開口部に対して、露光後の配線 のパターン形状が意図した形状と同一となるように、そ の幅に応じて前記補正とは別の補正を加えることを特徴 とするマスクパターン設計方法。

・【請求項7】 素子領域と配線のパターンデータを用い て論理演算を行うことによりレベンソンマスクとして複 数のパターンデータを発生し、前記レベンソンマスクの 連続して位置する複数の開口部を有するようにマスクバ ターンを設計するマスクパターン設計方法において、 前記レベンソンマスク上の連続して位置する前記複数の 開口部の中の最も外側の開口部の幅を、この開口部に隣 接するひとつ内側の開口部の幅と同一にし、

更に、前記複数の開口部の中の全ての開口部に対して、 露光後の配線のパターン形状が意図した形状と同一とな るように各開口部の幅に応じた補正を加えることを特徴 とするマスクパターン設計方法。

## ・【発明の詳細な説明】

$\cdot [0001]$

・【発明の属する技術分野】本発明は、半導体集積回路の 製造工程のひとつであるフォトリソグラフィ工程に使用 されるフォトマスクの設計に係り、特にロジックデバイ スのゲート電極の形成に使用されるマスクパターンの設 計方法に関する。

-[00002]

・【従来の技術】近年、半導体装置の製造においては、回 路を構成する素子や配線などの髙集積化、また微細化が 進められている。例えば、EWS (Engineering Work St ation)やPC (Personal Computer) のCPUとして用い られるRISCプロセッサの製造において、2002年 にはトランジスタのゲート電極の寸法として110nm が求められている。

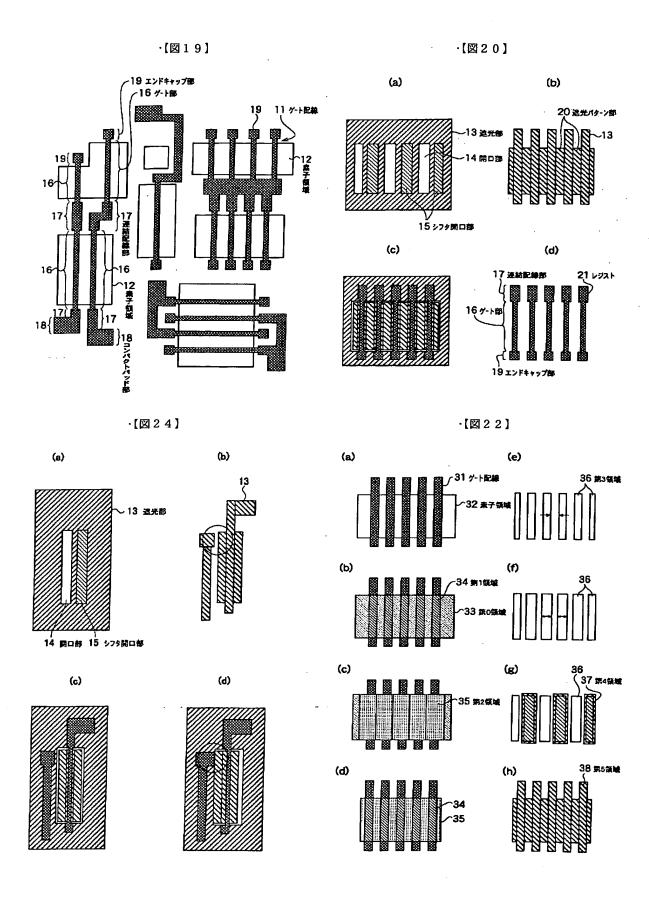

·【0003】RISCプロセッサのゲート及び素子領域 のパターン例を図19に示す。ここで、ゲート配線11 のゲート長を与えるのは素子領域12上に載った微細ゲ ート部16である。連結配線部17はこのゲート部16 とコンタクトパッド部18を接続する。ゲート配線11 は、エンドキャップ部19により終端している。

・【0004】ところで、近年の回路パターンの微細化に 伴い、フォトマスク上のパターンを半導体ウェハ上に転 写するフォトリソグラフィ工程におけるパターン転写精 度の低下が深刻になっている。

・【0005】この転写精度を向上させる手法のひとつ に、フォトマスクを通過する光の位相を変えることによ って、半導体ウェハ上に投影される像のコントラストを 向上させる位相シフトマスク露光法がある。

【0006】位相シフトマスクの中でレベンソン位相シ 数のパターンデータを発生し、その際、前記レベンソン 50 ワトマスクは、遮光領域を挟んで隣接する開口領域を通 過する露光光に180度の位相差を与えるように、一方 の開口に位相シフタを設けたものである。

-【0007】このレベンソン位相シフトマスクは上述し た線幅110nmのゲート部16をフォトリソグラフィ 技術で達成するために必須のものである。

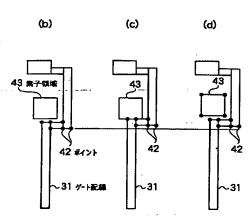

·【0008】図20(d)に示すようなゲートパターン の形成にレベンソン位相シフトマスクを用いる場合を考 える。このようなゲートパターンを形成する方法とし て、例えば特開平7-106227に示されるように、 レベンソン位相シフトマスクと通常のフォトマスクを多 10 重露光する方法がある。

·【0009】第1のフォトマスクとして、図20(a) に示すようにゲート部16を挟む開口14を設け、ゲー ト部16を挟んで交互に位相シフタ部15を設けたレベ シソン位相シフトマスクを用いる。

·【0010】第2のフォトマスクとして、図20(b) に示すように、連結配線部17とコンタクトパッド部及 びゲート部16を覆う遮光パターン部20を含む遮光パ ターン13を設けた通常のフォトマスクを用い、これら 第1、第2のフォトマスクを多重露光する。

·【0011】図20(c)に示すように遮光部の重なる 領域に露光光が照射されない暗部が形成され、従って、 ポジレジストを用いた場合には、図20(d)に示すよ うに暗部にレジスト21の残ったパターンが形成され る。ここで、第2の露光に使用したマスクはトリムマス クと呼ばれる。

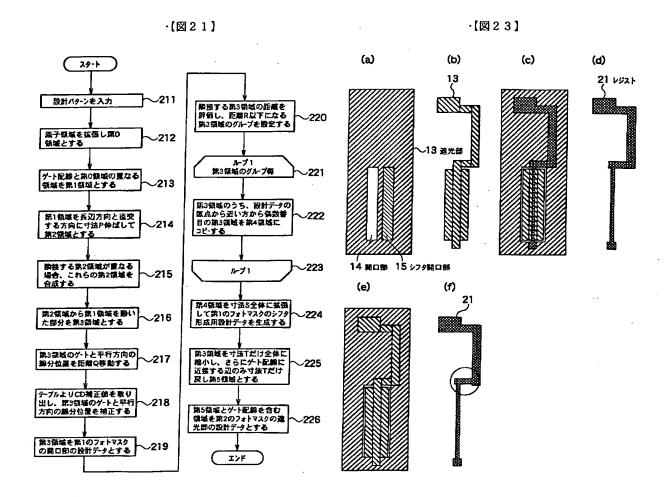

・【0012】これらレペンソンマスクとトリムマスクの パターンデータを設計する方法として、例えば以下の工 程がある。これを図21、図22を用いて説明する。図 21は従来の設計方法の工程を表すフローチャートであ 30 り、図22は前記工程に対応するフォトマスクの設計を 説明する要部上面図である。但し、ゲート部16はレベ シソンマスクにより、連結配線部17、コンタクトパッ ド部18及びエンドキャップ部19はトリムマスクによ り形成される。

・【0013】図21に示したステップ211にて、ま ず、図22(a)に示すようにゲート配線31と素子領 域32の元の設計パターンを入力する。次に、ステップ 212にて、図22 (b) に示すように素子領域12を 拡張して第0領域33とする。ここで、素子領域32を 40 拡張するのは、微細ゲート部を素子領域32より少し張 り出した設計とするためである。これは、素子領域32 に微細ゲート部より幅の広い連結配線部が載るとトラン ジスタの性能が劣化するため、マージンをみて少し張り 出させる。

-【0014】次に、ステップ213にて、ゲート配線3 1と第0領域33の重なる領域を算出して、第1領域3 4とする。ここで、最終的に第1領域34の幅を減じた 領域が微細ゲート部になる。ステップ214にて、図2 2 (c) に示すように、第1領域34をゲート部31と 50 域37とする。その後、ステップ224に示すように、

直交する方向に予め設定した値Pだけ伸ばして第2領域 35とする。

・【0015】その後、ステップ215にて、図22 ·(d) に示すように、第2領域35が隣接する第2領域 35と重複するものについてはこれを合成し、ステップ 216にて、第2領域35から第1領域34を除いた領 域を演算により求め、図22(e)に示すように第3領 域36とする。

·【0016】次に、ステップ217にて、図22(f) に示すように第3領域36の短辺方向の幅を狭めるよう に、第3領域36の辺の位置を距離Qだけ移動させる。 これにより、所望サイズの微細ゲート部の設計を行う。 ·【0017】次に、ステップ218にて、第3領域36 に対して、OPC (Optical Proximity Correction) 処理 を施す。OPC処理を施さないと、図19のゲート配線 16のように、様々な間隔でパターンが存在する場合 に、ゲート部の幅が均一に仕上がらないという現象が生 じる。

·【0018】即ち、フォトマスク上のサイズAのパター シを転写する場合、被加工基板上のレジストを所望サイ ズ(A/露光倍率)に仕上げるように露光時の露光量を 設定したとすると、サイズBのパターンが所望値(B/ 露光倍率) からずれて形成される。従って、ゲート部の 幅を所望値に形成するように、フォトマスクの設計パタ ーンサイズに開口幅に応じた補正をかける必要がある。 ・【0019】例えば、予め実験よりフォトマスク上の第 3領域36の幅 (開口幅) に対して、レジストの仕上が り寸法を測定し、補正テーブルを用意し、これにしたが って補正を行う方法がある。若しくは、シミュレーショ シにより第3領域36の幅に応じてレジストの仕上がり 寸法を予測する方法もある。

【0020】しかしながら、実験的に補正をかけた方 が、レジストパターンを形成した後の、ゲート電極のR ·IE (Reactive Ion Etching) の工程における寸法変換 差を含む補正ができ、より髙精度の補正が可能である。 その後、ステップ218を経てステップ219にて、第 3領域36をレベンソンマスクの開口部14の設計パタ ーンとする。

・【0021】次に、レペンソンマスク作製におけるシフ タパターンの設計を図22(g)に示すようにステップ 220~224で行う。まず、シフタパターンを開口部 14に交互に配置するためにステップ220~223の 工程を行う。ここでは、隣接する第3領域36間の距離 を評価し、距離R以下になる第3領域36のグループを 求める。

・【0022】更に、ステップ221~223において、 このグループ毎に、例えば設計上の原点の位置から近い 側から0°、次に180°、0°、180°と交互にシ フタ配置を決定する。そして、180°の領域を第4領

レベンソンマスク作製時のシフタパターンの描画データ を設計するために、寸法Sだけ全体に太らせる。

・【0023】次に、ステップ225、226にて、図22(h)に示すようにトリムマスクの設計として、第3領域36を距離Tだけ僅かに縮小し、これとゲート配線31のパターンの両方を含むパターンデータを作成し、これをトリムマスクの遮光部の設計パターンとする。第3領域36を縮小するのは、レベンソンマスクとトリムマスクの露光時の合わせずれ(アライメント誤差)を考慮した結果である。

#### $\cdot [0024]$

・【発明が解決しようとする課題】しかしながら、上記した従来のマスクパターンの設計方法には以下の問題がある。図23(a)~(c)に示すように、開口部と連結配線の間隔が狭い場合には、多重露光時のアライメント誤差により連結配線の幅が細る、若しくは太る場合がある。図23(a)にレベンソンマスクの設計パターンを、図23(b)にトリムマスクの設計パターンを示す。アライメント誤差がない場合には、図23(c)に示すような多重露光のイメージになり、図23(d)に 20 示すように、所望のパターンが形成される。

・【0025】しかしながら、図23(e)に示すように、レベンソンマスクに対してトリムマスクの位置が下方向にずれて露光された場合、図23(f)に示すように、連結配線部(図中円内の部分)の寸法が細る問題がある。一般にデバイスの性能に与える影響を考慮して、寸法の制御性として求められるのは寸法設計値±10%である。これに対してアライメント誤差ははるかに大きい。従って、図23のような場合には、アライメント誤差分の寸法誤差が生じるが、これは寸法の制御性として30許容できる値ではない。

・【0026】また、図24(a)~(e)に示すように、ゲート部に対して直交する方向に開口部14と連結配線の間隔が狭い場合も考えられる。図24(a)はレベンソンマスクの設計パターン、図24(b)はトリムマスクの設計パターンである。この場合には、図24・(b)中の円内に示すように、トリムマスクに近接した遮光パターンが生じる。図24(c)に所望のパターンを示す。

・【0027】しかしながら、図24(b)の円内の近接 40 部分が解像限界以下の距離である場合には、近接部分が繋がった遮光部となってしまう。そこで、多重露光後には図6(d)に示すように、コンタクトパッド部の寸法がレベンソンマスクの開口部の境界で決定されることになる。

·【0028】このため、コンタクトパッド部が意図した 寸法より大きく形成されることが考えられ、また両マス クの露光間におけるアライメント誤差により寸法が変動 する。

·【0029】OPC方法として開口幅を補正し、ゲート 50

6

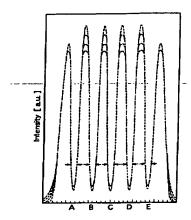

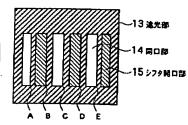

部の寸法を均一にしている。しかしながら、図25に示したゲート部A、Eのように、開口部14を挟んで隣に大面積の遮光領域13が存在する場合には、開口幅の補正が十分でない。

【0030】図26に図25のレベンソンマスクの設計パターンを被加工基板上に転写した時の投影像を示す。ゲート部B、C、Dは投影像のプロファイルがほとんど同じであり、解像線幅44がほぼ等しくなる。しかしながら、外側のゲート部A、Eについては内側のゲート部B、C、Dと異なる(狭くなる)ことがわかる。

【0031】このように、開口幅が全く同じでも周辺の環境によって、転写後の寸法が異なってくる。しかしながら、従来方法では、開口幅の補正を更に外側の環境を考えて補正していなかった。また、シミュレーションにより周辺の環境まで考慮して補正をかける方法もあるが、上述のように精度に乏しく、更に計算時間が膨大であるという問題がある。

・【0032】本発明は、上述の如き従来の課題を解決するためになされたもので、その目的は、容易にアラインメント誤差による連結配線部の寸法変動を無くすことができ、又、容易にゲート部の制御性を向上させることができるマスクパターンの設計方法及びこの設計方法により設計したマスクパターンを用いて製造した半導体装置を提供することである。

#### $\cdot [0033]$

・【課題を解決するための手段】上記目的を達成するために、請求項1の発明の特徴は、素子領域と配線のパターシデータを用いて論理演算を行うことにより複数のパターンデータを発生させることによりマスクパターンを設計するマスクパターン設計方法において、前記素子領域に予め設定した距離以下に近接する配線の一部又は全部を前記設定距離以上になるように遠ざける処理を含むことにある。

·【0034】この請求項1の発明によれば、例えば微細ゲート部と連結配線が近接する領域では連結配線を予め設定した距離以上に遠ざけるため、露光時、前記連結配線部の寸法が細るという問題を回避でき、所望のパターシを得ることができる。

【0035】請求項2の発明の特徴は、前記遠ざける処理を施した配線の一部又は全部に前記設定距離以下に近接するデバイスの構成要素があるかどうかを検出し、検出された場合は遠ざける処理を施した前記配線の一部又は全部から該当のデバイスの構成要素を前記設定距離以上遠ざける処理を行い、その後、前記遠ざける処理を施したデバイスの構成要素に前記設定距離以下に近接するデバイスの他の構成要素があるかどうかを検出し、検出された場合は該当のデバイスの構成要素を先に遠ざけたデバイスの構成要素から前記設定距離以上遠ざける処理を行うことを、前記設定距離以下に他のデバイスの構成要素が検出されなくなるまで、繰り返し行う処理を含む

ことにある。

・【0036】請求項3の発明の特徴は、前記素子領域に 配線の一部又は全部が前記設定距離以下近づいている場 合にこれを遠ざける処理を、前記素子領域いずれかの領 域に近接する線分を求め、該線分上に位置する図形の角 のポイントを含み該近接する線分から予め設定した距離 以下に位置する図形の角のポイントを抽出し、これを近 接する方向に平行に移動させるアルゴリズムにより行う ことにある。

·【0037】請求項4の発明の特徴は、素子領域と配線のパターンデータを用いて論理演算を行うことにより複数のパターンデータを発生させることによりマスクパターンを設計するマスクパターン設計方法において、予め設定した距離以下に素子領域と配線の一部又は全部が近づいている場合には、該配線の少なくとも一部に対に近接している開口を拡張するか、該配線に近接して新たな開口を設けるパターンデータを発生させる処理を含むことにある。

・【0038】請求項5の発明の特徴は、前記設定距離以下に素子領域と配線の一部又は全部が近づいている場合には、該配線の少なくとも一部に近接している開口を拡張するか、該配線に近接して新たな開口をレベンソンマスクとして形成するパターンデータを発生させる処理を含むことにある。

・【0039】請求項6の発明の特徴は、素子領域と配線のパターンデータを用いて論理演算を行うことによりレベンソンマスクとして複数のパターンデータを発生し、その際、前記レベンソンマスクの連続して位置する複数の開口部に対して、各開口部の幅に応じて補正を加えてマスクパターンを設計するマスクパターン設計方法にお30いて、前記開口部の最も外側の開口部に対して、露光後の配線のパターン形状が意図した形状と同一となるように、その幅に応じて前記補正とは別の補正を加えることにある。

·【0040】この請求項6の発明によれば、前記最も外側の開口部の幅を、隣接する内側の開口部の幅に例えば合わせるようにOPCを用いて前記別の補正を加えることにより、前記全ての開口部の幅を揃えることができ、これにより例えばゲート部の寸法制御性が向上する。

・【0041】請求項7の発明の特徴は、素子領域と配線 40でパターンデータを用いて論理演算を行うことによりレベンソンマスクとして複数のパターンデータを発生し、前記レベンソンマスクの連続して位置する複数の開口部を有するようにマスクパターンを設計するマスクパターシ設計方法において、前記レベンソンマスク上の連続して位置する前記複数の開口部の中の最も外側の開口部の幅を、この開口部に隣接するひとつ内側の開口部の幅と同一にし、更に、前記複数の開口部の中の全ての開口部に対して、露光後の配線のパターン形状が意図した形状と同一となるように各開口部の幅に応じた補正を加える 50

ことにある。

$\cdot [0042]$

・【発明の実施の形態】以下、本発明のマスクパターンの 設計方法の実施の形態を図面に基づいて説明する。但 し、以降説明する各パターン等の寸法値は被加工基板上 の寸法値を示しており、フォトマスク上ではその4倍の 値である。

8

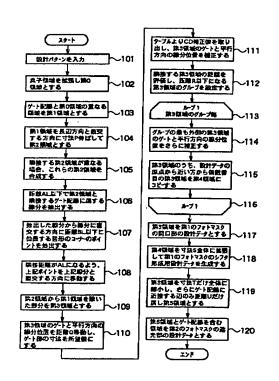

·【0043】 実施例1

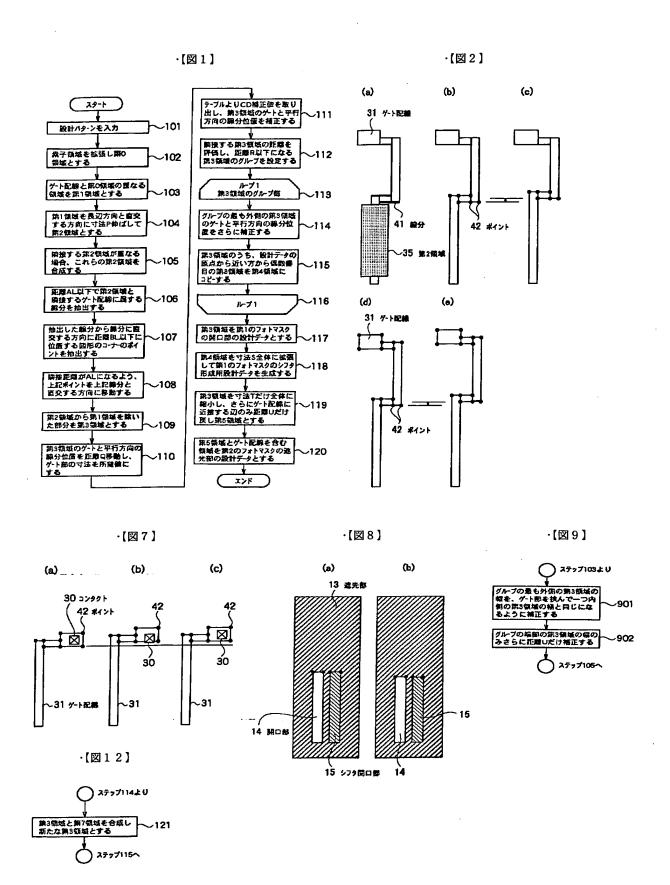

図1は本発明の実施例1のマスクパターンの設計方法の 工程を説明するフローチャートである。このフローチャ ートでは、レベンソンマスクとトリムマスクの設計方法 を説明している。図2は上記設計方法を説明するフォト マスクの要部上面図である。

・【0044】図1のステップ101にて、まず、ゲート配線と素子領域の元の設計パターンを入力した。ここで、ゲート配線の元の設計寸法は240nmであり、以下の工程で、被加工基板上で所望値110nmのゲート部寸法を得るようフォトマスクの設計を行った。

・【0045】ステップ102にて、素子領域を拡張し第 0領域とし、次に、ステップ103にて、ゲート配線と 第0領域の重なる領域を算出し、第1領域とした。ここ で、最終的に第1領域の幅を減じた領域が微細ゲート部 になる。

・【0046】ステップ104にて、第1領域をゲート部と直交する方向に予め設定した値Pだけ伸ばして第2領域とした。ここで、Pは150nmとした。次に、ステップ105に示すように、第2領域が隣接する第2領域と重複するものについてはこれを合成した。

・【0047】その後、ステップ106~108にて、ゲート部と距離AL以下に近接する連結配線を抽出し、これをゲート部から遠ざけるよう設計を変更する処理を行った。ここで、距離ALは予め設定された基準値である。

・【0048】まず、ステップ106、107にて、距離 AL以下で第2領域と近接する連結配線部を抽出し、これを含むポイントを移動させるポイントとして設定する。

・【0049】これについては図2を用いて説明する。即ち、図2(a)に示すように第2領域35とゲート配線31の設計パターンとの近接距離(第1領域の長辺方向)を評価して、その時、距離AL以下に近接するゲート配線の図形の辺(線分)41を抽出した。図2(b)はゲート配線31の設計パターンの図形を示している。この図2(b)に示すように、上記近接する辺を含む図形のコーナーのポイントの内、第1領域の長辺方向の距離がBL以下となるポイント42を抽出した。ステップ108にて、図2(c)に示すように上記辺の近接距離が距離ALとなるようにポイント42を移動させた。これには、ステップ106の処理時点での近接距離と距離ALとの差を算出しておき、差の距離BLを移動させれ

ばよい。尚、エンドキャップ部19については、その幅、長さの変動がデバイスの性能にほとんど影響しないため、処理の対象から除外している。

·【0050】次に、ステップ109に示すように、第2 領域から第1領域を除いた領域を演算により求め、第3 領域とした。

・【0051】その後、ステップ110に示すように、第3領域の短辺方向の幅を狭めるように、第3領域の辺の位置を距離Qだけ移動させる。これにより、所望サイズ110nmの微細ゲート部の設計とした。ここで、距離10Qは元のゲート配線の寸法240nmからゲート部の寸法110nmを引いた差である130nmの半分65nmである。

・【0052】次に、ステップ1111にて、上記第3領域 ・(開口幅) に対して、1度目のOPC (Optical Proximity Correction) 処理を施して開口幅の補正を行う。

・【0053】予め実験よりフォトマスク上の第3領域の幅(開口幅)に対して、ゲート配線のRIE後の仕上がり寸法を測定し、図17の表図に示した補正テーブルを用意した。ゲート配線の形成工程については後述する。・【0054】ここで、図17の表図の補正値は開口幅の片側の辺に対して与える補正値である。例えば、開口幅450nmの開口では開口幅を片側で30nmに補正する。即ち、450nmから30nm×2を太らせて510nmとする。

・【0055】次に、2度目のOPC処理及びレベンソンマスク作製におけるシフタパターンの設計をステップ112~116で行う。

·【0056】まず、隣接する第3領域間の距離を評価 し、距離R以下になる第3領域のグループを求めた。こ こで、距離Rは400nmとした。

・【0057】次に、ステップ114に示すように、第3領域のグループにおいて、開口部の両側の遮光部の寸法を評価し、グループの中で最も外側にある開口部を抽出した。そして、上記開口について2度目の補正を施した。

・【0058】ここで、最も外側の開口幅は、P(150 nm)からステップ110の工程を経て280nmに、更にステップ111の補正を経て300nmになっている。更に図18の表図に示す補正値を与え、結果的に内 40 部の開口幅が510nmの場合には、最も外側の開口幅を片側で10nm細らせて結果的に280nmとした。・【0059】図18の表図に示す補正値はグループの最も外側の開口幅が300nmの時の値であり、図17の表図と同じく実験結果より求めたものである。外側の開口幅を変化させると、補正値も変更する必要がある。・【0060】その後、ステップ115に示すように、シッタパターンをグループ内の開口に対して交互に配置した。例えば設計上の原点の位置から近い側から偶数番目をシフタとし、第4領域とした。

10

【0061】次に、ステップ117を経て第3領域をレベンソンマスクの開口部の設計パターンとした。

・【0062】更に、ステップ118に示すように、レベシソンマスク作製時のシフタパターンの描画データを設計するために、第4領域を寸法Sだけ全体に太らせた。ここでは、前記Sを所望のゲート部の寸法110nmの約半分の50nmとした。

【0063】更に、ステップ119、120に示すように、トリムマスクの設計として、第3領域を距離Tだけ僅かに縮小し、これとゲート配線31のパターンの両方を含むパターンデータを作成して、これをトリムマスクの遮光部の設計パターンとした。ここで、前記Tはアライメント誤差を考慮し、30nmとした。以上のように、レベンソンマスクとトリムマスクの設計を行った。【0064】次に、上記した設計方法により設計したフォトマスクを用いた半導体装置の製造方法について図3を参照して説明する。

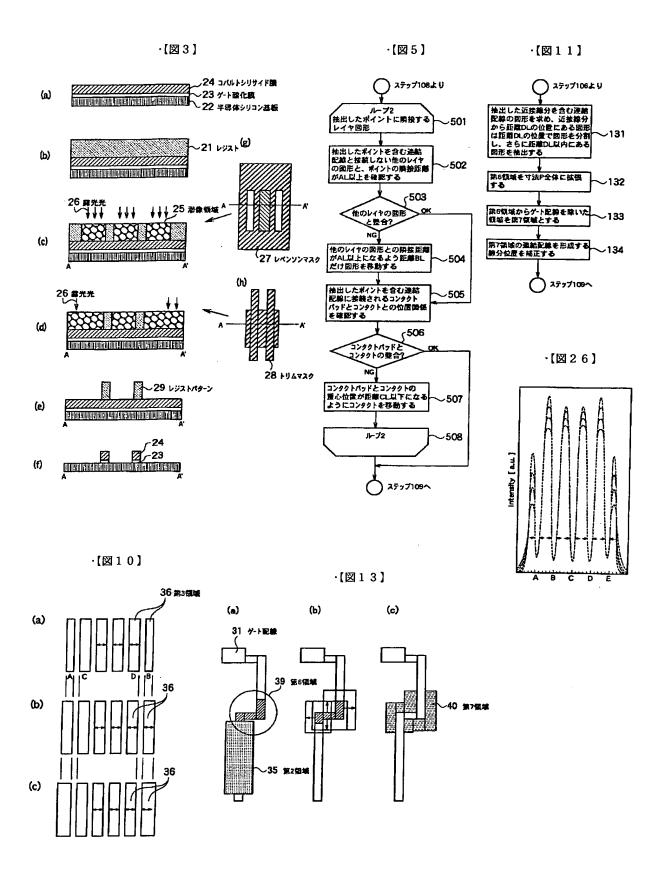

・【0065】図3は(a)~(h)はゲート配線の形成 工程を示す半導体基板の要部断面図である。図3(a) に示すように、Siウェハ(半導体シリコン基板)22 上に厚さ3nmのゲート酸化膜23を形成し、更にその 上に厚さ160nmのポリシリコン膜24を積層して形成した。

·【0066】次に、図3(b)に示すように、ポジレジ スト21を厚さ240nmに調整して基板全面に塗布 し、塗布後、ペーク(Bake)を90℃、120secの 条件で行った。

・【0067】更に、図3(g)に示した上述の方法で設計したレベンソン位相シフトマスク27を用いて、図3・(c)に示すように、第1の露光を行い、レジストに潜像を形成した。ここで、潜像とは、露光光を照射されることによりマスクの投影像に応じてレジストの化学反応が引き起こされた領域のことである。

·【0068】露光条件は、スキャナー型の露光装置(波長248nm)を用いて、NA(開口数)を0.5、σ·(コヒーレンシー)を0.3の照明条件とした。

・【0069】その後、図3(h)に示した上述の方法で設計したトリムマスク28を用いて、図3(d)に示すように第2の露光を行った。露光条件は、露光装置として第1の露光と同じものを使用して、照明条件をNA0.55、 $\sigma$ を外形が0.8で、内径0.53が遮蔽された2/3の輪帯照明で行った。

【0070】次に、図3(e)に示すように、基板を露 光装置より搬出し、露光後ペーク(PEB:Post Expos ure Bake)を110℃、120secの条件で行った 後、アルカリ現像液を用いて現像し、感光部のレジスト を溶解させてレジストパターン29を形成した。

・【0071】更に、図3(f)に示すように、レジスト パターン29をマスクに弗素を含むガスを用いたRIE (Reactive Ion Etching)を行い、ポリシリコン膜24と ゲート酸化膜23のパターンを形成した。

・【0072】その後、図示しない窒化シリコン膜を成膜 する等の工程を経て、半導体装置を製造した。

·【0073】ここで、実施例1で用いた露光装置のアラ イメント誤差は最大60nmである。寸法の制御性とし て求められるのは、ゲート部の寸法が所望値110nm に対して±11nm、また、連結配線部は所望値240 nmに対して±24nmである。従って、連結配線部と ゲート部が近接している場合には、アライメント誤差に より寸法制御性の要求値以上に連結配線部の寸法が変動 10 する可能性がある。

-【0074】本実施例によれば、図1のステップ106 ~108の処理により、近接する連結配線部を遠ざける ように設計パターンを変更し、これによりアライメント 誤差による連結配線部の寸法変動をなくすことができ る。

・【0075】また、元の開口幅に応じて開口幅の補正を 加えるOPCを行い、更に、開口を挟んで隣に大面積の 遮光領域が存在する上記グループの最も外側の開口幅に 対して図1のステップ114の処理により第2のOPC を行うことによって、更なる補正を加えているため、図 4の第2のOPC後のレベンソンマスクの設計パターン の投影像プロファイルに示されるように、ゲート部A~ Eまでの幅を揃えることができる。

・【0076】このように、第2の〇PC工程を付加する ことにより、ゲート部の制御性をより向上させることが 可能となった。また、RIE後の寸法値を実験により測 定して補正値を決定しているため、精度を高くすること ができる。更にシミュレーションを用いる補正に比べ、 はるかに短い時間で容易に設計を完了することができ る。

## ·【0077】実施例2

図5は本発明の実施例2の設計工程の要部を示したフロ ーチャートである。この実施例2は実施例1で説明した 図1の設計工程のステップ108とステップ109の間 に図5に示した工程を挿入して、全体の工程が構成され ている。ところで、上記実施例1の図1に示したステッ プ106~108においてゲート部と近接するゲート配 線のパターン設計を変更し、近接図形を移動させた。

・【0078】しかしながら、デバイスの設計パターンに 40 よっては、設計変更により不都合を生じる場合がある。 例えば、連結配線やコンタクトパッド部の移動先に極め て近接した位置に他のレイヤのパターン、例えば素子領 域やコンタクトがある場合には、ショート等の問題が生 じることが懸念される。また、コンタクトパッド部を移 動させるとコンタクトとの位置ずれが生じたり、コンタ クト抵抗が増加することが懸念される。このようなこと を回避するために、本例では図5に示した設計工程を加 えている。

プ108にて移動したポイントに近接するゲート以外の レイヤの図形を抽出する。この時、近接距離はおよそA L以上に設定すればよい。次にステップ502にて、前 記抽出した図形と前記ポイントとの隣接距離がAL以上 かどうかを調べて、ステップ503にて、他のレイヤの 図形と整合性がとれているかを判断する。他のレイヤの 図形が近接距離内に存在しない場合には、他のレイヤと の整合性がとれていると判断して、ステップ505に進

・【0080】他のレイヤの図形が存在する場合には、ス テップ504にて、前記ポイントとの隣接距離がAL以 下の図形も距離BL移動させる。この状態は図6(a) ~ (d) に示されている。

·【0081】図6(a)は所望のパターンを示してい る。図6(b)に示すように、元々の設計データにおい て素子領域43がゲート配線31と近接している場合 に、近接するポイント42を抽出し、図6(c)に示す ようにポイント42を移動させる。この時、移動させた 図形のポイント42と近接する素子領域43についても 抽出して、これを図6 (d) に示すように移動する工程 が加えられている。

・【0082】上記のように移動させた図形に対して近接 距離内に他のレイヤの図形がないかを更に調べ、存在す る場合には該当の図形を移動させる。このような図形の 移動処理を繰り返し、最終的に、移動した図形の近接距 離以内に他のレイヤの図形がないと確認され、ステップ 503で他のレイヤの図形と整合性がとれたと判断され るまで行う。

・【0083】次にステップ505にて、抽出したポイン トを含む連結配線に接続されるコンタクトパッドとコン タクトの位置関係を確認する。その結果、図7 (a) に 示すように、移動したポイント42がコンタクトパッド 部のポイントを含む場合、ステップ506にて、コンタ クトパッド部とコンタクト30との位置の整合性がとれ ているかどうかを判断する。整合性がとれている場合は 図1のステップ109へ進み、図7(b)に示すように 整合性がとれていない場合は、ステップ507にて、図 7(c)に示すようにコンタクト30を距離BL移動さ せる。

・【0084】本発明によれば、実施例1と同様に、近接 する連結配線部を遠ざけるように設計パターンを変更 し、これにより、アライメント誤差による連結配線部の 寸法変動をなくすことができる。

·【0085】又、連結配線部に接続されるコンタクトパ ッド部18を移動するように設計変更を行った際に、こ れと接続されるコンタクト30のパターンを同様に移動 させることにより、コンタクトパッド部とコンタクト3 0の位置ずれにより生じるコンタクト抵抗の増加による デバイス性能の劣化を防止することができる。

·【0079】まず、ステップ501では、図1のステッ 50 ·【0086】更に、連結配線部或いはコンタクトパッド

部が移動したために、これらが素子領域等に近接して、 ショートなどのデバイス性能の劣化が懸念されるが、こ れに対して、移動した配線図形の周辺にあるゲート以外 のレイヤの図形を抽出し、これを同様に移動させること を繰り返して行って、異常接近した素子領域等を無くす ことができ、前記配線図形の移動によるデバイス性能の 劣化を防止することができる。

#### ·【0087】実施例3

図8は本発明の実施例3の要部を示した平面図ある。上 記した実施例1、2によれば、連結配線部及びコンタク トパッド部の位置を移動させることにより、アライメン ト誤差による連結配線部の寸法変動を防止し、又、前記 移動によるデバイス性能の劣化を防止している。

・【0088】しかし、デバイス性能の許す範囲で第3領 域の設計パターンの辺の位置を移動させ、延いては本例 の図8のようにレベンソンマスクの開口部の設計パター シの辺の位置を変更してもよい。図8(a)は、変更前 の開口部14とシフタ開口部15の辺の位置を示してお り、図8 (b) に変更後の開口部14とシフタ開口部1 5 の辺の位置を示している。この場合には、ゲート部の 長さが短くなるため、これに合わせて素子領域の設計パ ターンの辺の位置も移動させることが望ましい。

・【0089】本実施例によれば、近接するゲート部を遠 ざけるように設計パターンを変更することにより、実施 例1、2と同様に、アライメント誤差による連結配線部 の寸法変動をなくすことができる。

## ·【0090】実施例4

図9は本発明の実施例4の要部を示したフローチャート である。上記実施例1では、開口部のグループの最も外 側の開口幅を図1に示したステップ114の第2のOP C工程を行うことによって補正したが、本例のように前 記第2のOPC工程を図9のフローチャートに示すよう な工程で行っても良い。

・【0091】図9のステップ901にて、まず、図10 ·(a) に示す第3領域36のパターンに対してグループ の最も外側 (A、B) の第3領域36の幅を、図10 ·(b) に示すようにゲート部を挟んで隣に位置(C、 D) する第3領域36の幅と同じに補正する。

·【0092】次にステップ902にて、図10(c)に 示すように最も外側の第3領域36の幅を更に実験的に 40 求めた距離Uだけ外側に広げて補正する。但し、本例で は距離Uは50nmとした。

・【0093】本実施例によれば、グループの最も外側に 位置する開口A、B間のゲート部を開口C、D間等の内 側のゲート部の寸法と揃えるように、実験的に求めた距 離 U広げて補正することにより、実施例1と同様に、ゲ ート部の寸法を揃えることができるばかりではなく、ゲ ート部の制御性をより向上させることができる。

·【0094】実施例5

14

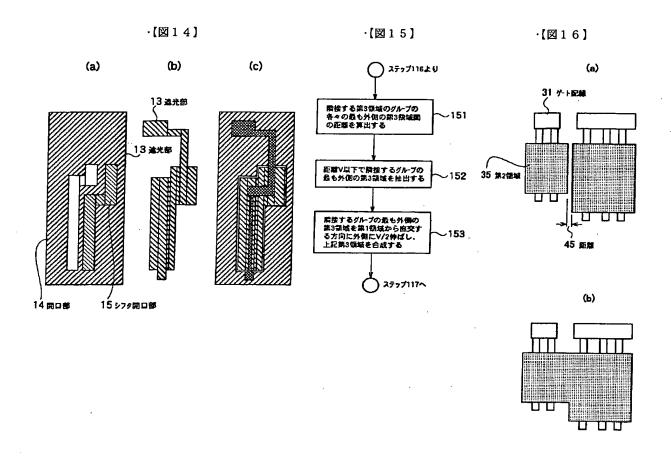

ートである。本例はレベンソンマスクとトリムマスクの 設計方法の別の例を示したものであり、図11はその設 計方法の工程を示したものである。図13は前記設計方 法を説明するフォトマスクの要部上面図であり、図14 は設計後のフォトマスクの要部断面図である。

・【0095】以下に本実施例を説明する。実施例1の図 1に示したステップ106~108にて、ゲート部と近 接するゲート配線のパターン設計を変更して、近接図形 を移動させが、本例では、近接する連結配線部をレベン ソンマスクで形成するようにパターン設計するものであ る。これに伴い、図1のステップ107、108を図1 1に示す設計工程に変更する。

·【0096】図1のステップ106にて、距離AL以下 で第2領域35と近接するゲート配線31の線分を抽出 した。その後、本例のステップ131にて、図13 ·(a) に示すようにその線分から距離DLにある上記近 接するゲート配線31を構成する図形を抽出し、同図 ·(a) の円で示した部分を第6領域39とした。ここ で、距離DLの位置に跨がってゲート配線を構成するあ る図形が存在する場合には、その図形を距離DLの位置 で分割した。但し、DLは600nmとした。 ·【0097】次のステップ132にて、距離DL以内の

図形を寸法Pだけ全体に拡張した。ここで、寸法Pは実 施例1と同様に150nmとした。この状況を図13 ·(b) の矢印で示す。その後、ステップ133にて、図 13 (c) に示すように、上記図形からゲート配線を除 いた領域を演算により求め、第7領域40とした。 ・【0098】更に、次のステップ134にて、図1のス テップ111においてゲート部の寸法にOPC処理を加

えたと同様に、ゲート部に対してもOPC処理を加え る。実施例1のステップ111では図17の表図に示す 補正値にしたがって補正を加えたが、ここでは、新たな 補正テーブルを用意し、これにしたがって補正を行っ た。

・【0099】更に、図1に示すステップ114とステッ プ115間に、図12に示すステップを挿入した。すな わち、第3領域と上記の設計工程により新たに生成した 第7領域を合成し、新たな第3領域とした。その後、図 1に示す諸々の工程を経た後、第3領域を第1のフォト マスクの開口部の設計データとした。

・【0100】以上の設計工程を終了した段階でのフォト マスクは図14のようになる。ここで、図14 (a) は. レベンソンマスクの、図14(b) はトリムマスクの、 図14(c)はこれらマスクを多重露光して得られる露 光イメージの要部上面図である。図14(c)は露光後 に得られるゲート部を示した上面図である。図14 ·(a) に示すとおり、レベンソンマスクの開口部が微細 ゲート部のみならず、連結配線部に伸びていることがわ かる。

図11、図12は本発明の実施例5を示したフローチャ 50 【0101】本実施例によれば、近接する連結配線部を

レベンソンマスクで形成するように設計パターンを変更 して、アライメント誤差による連結配線部の寸法変動を なくすことができる。アライメント誤差によりレベンソ シマスクとトリムマスクの連結部分で配線の位置ずれが 生じるが、これは性能上問題にならないので、無視して 良い。

・【0102】(追記1)一般に、プロセッサの設計においてSRAM等のメモリが設計パターンに存在する場合、メモリ部分に関してはあるセルパターンが数メガ個といった繰り返しで設計される。このように同一セルパターンの繰り返しパターン部分については別の条件(例えば、距離P、R等)を用いてパターンの設計変更を行ってもよいし、実施例1~実施例5の設計工程によらず、手動でセルパターンを変更するといった操作を行ってもよい。

・【0103】(追記2)図2(d)に示すように、第2領域と近接する辺を含み、第2領域から離れる方向に存在する図形全てを、第2領域と上記辺の近接距離がALになるだけ、移動させることにより、図2(e)に示すようにパターンを変更してもよい。この時、当然ながら図2(d)に示す図形に接続されない他の図形は処理しないことになる。

・【0104】(追記3)上記実施例1~実施例5で説明したパターン設計方法では、微細ゲート部を所望値に形成するために、OPCを施すことにしている。連結配線部はトリムマスクを用いて形成されるが、連結配線部の寸法制御性を向上させるために、トリムマスクのパターシ、上述の設計方法ではゲート配線の領域に対してOPCをかける工程を加えてもよい。これにより、連結配線部の寸法制御性をも向上させることができる。

・【0105】(追記4)図15に示すような工程を実施例1のステップ116とステップ117の間に挿入してもよい。第3領域からレベンソンマスクの開口部の設計パターン及びトリムマスクのゲート部を覆う領域のパターンを作成する。ステップ151にて、隣接する第3領域のグループの各々の最も外側の第3領域の間の距離を算出する。

・【0 1 0 6】その結果、例えば、図16(a)に示すように、レベンソンマスクの開口部のグループ間の距離 4 5がV以下に近接している場合には、次の問題が生じる 40 可能性がある。

·【0107】例えば、Vを100nmとすると、フォトマスク上の寸法はその4倍の400nmである。フォトマスク上400nm以下のような微細なパターンを作製する場合、フォトマスク作製に使用するEB(Electron Beam) 描画装置の性能によってはパターンが解像されない場合がある。

·【0108】このような描画装置の解像限界以下のパターンをフォトマスク上の設計データとして存在させるべきではない。

16

【0109】そこで、ステップ152にて、距離V以下で隣接するグループの最も外側の第3領域を抽出し、ステップ153にて、隣接するグループの最も外側の第3領域を第1領域から直交する方向で外側にV/2伸ばし、上記第3領域を合成する。その結果は図16(b)に示され、グループの最も外側の第3領域を外側に、即ち、ゲート部と直交する方向に広げて両グループの外側の第3領域を合成する。これにより、レベンソンマスクの開口パターン及びトリムマスクの遮光パターンの近接するグループを拡張して合成させることになり、描画装置の解像限界以下のパターンがフォトマスク上に存在しなくなる。

・【0110】(追記5)上記実施例1〜実施例5において、第1のフォトマスクであるレベンソン位相シフトマスクのパターンと第2のフォトマスクであるトリムマスクのパターン設計方法について述べた。ところで、第1のフォトマスクのパターンと第2のフォトマスクのパターンを1枚のフォトマスク内の異なる領域に配置してもよい。

20 【0111】1枚のマスクに両パターンを形成することにより、多重露光時のアライメント誤差を低減することができる。

・【0112】その他、本発明のバターン設計方法に関して、本発明の主旨を逸脱しない限り、含まれる工程の順 序を入れ替えても、同様の効果を得ることができる。

$\cdot [0113]$

·【発明の効果】以上詳細に説明したように、本発明によれば、アラインメント誤差による連結配線部の寸法変動を無くすことができ、又、ゲート部の制御性を向上させることができる。

・【図面の簡単な説明】

・【図1】本発明の実施例1のマスクパターンの設計方法 の工程を説明するフローチャートである。

·【図2】上記実施例1のフォトマスクの設計を説明する 要部上面図である。

·【図3】上記実施例1のゲート配線の形成工程を説明する半導体基板の要部断面図である。

·【図4】上記実施例1のフォトマスクの投影像のプロファイルを示す図である。

10 【図5】本発明の実施例2のフォトマスクの設計工程の 要部を説明するフローチャートである。

·【図6】上記実施例2のフォトマスクの設計を説明する要部上面図である。

・【図7】上記実施例2のフォトマスクの設計を説明する他の要部上面図である。

·【図8】本発明の実施例3のフォトマスクの設計工程を 説明する上面図である。

·【図9】本発明の実施例4のフォトマスクの設計工程を 説明するフローチャートである。

**50 ·【図10】上記実施例4のフォトマスクの設計を説明す**

る図である。

- ・【図11】本発明の実施例5のフォトマスクの設計工程 を説明するフローチャートである。

- ·【図12】上記実施例5を説明するフローチャートである。

- ・【図13】上記実施例5のフォトマスクの設計工程を説明する要部上面図である。

- ·【図14】上記実施例5のフォトマスクの設計を説明する要部上面図である。

- ·【図15】本発明のその他のフォトマスクの設計工程を 説明するフローチャートである。

- ·【図16】本発明のその他のフォトマスクの設計工程を 説明する要部上面図である。

- ·【図17】 実施例1のフォトマスクの設計工程における 第1の寸法補正値を示す表図である。

- ·【図18】実施例1のフォトマスクの設計工程における 第2の寸法補正値を示す表図である。

- 【図19】従来のRISCプロセッサのゲート配線のパターン例を示す要部上面図である。

- ·【図20】従来のゲート配線の形成用に用いられる多重 20 露光用のフォトマスクを説明する要部上面図である。

- ·【図21】多重露光用のフォトマスクの従来の設計工程を説明するフローチャートである。

- ·【図22】多重露光用のフォトマスクの従来の設計による製造工程を説明する要部上面図である。

- ・【図23】多重露光用のフォトマスクの従来の設計の問題点を説明する図である。

- ·【図24】多重露光用のフォトマスクの従来の設計の問題点を説明する図である。

- ・【図25】多重露光用の従来のフォトマスクの設計パタ <sup>30</sup> ーンを示した図である。

- ·【図26】図25に示した設計パターンのプロファイルを示した投影図である。

\*・【符号の説明】

- 11、31 ゲート配線

- 12、32、43 素子領域

- 13 遮光部

- 14 開口部

- 15 シフタ開口部

- 16 ゲート部

- 17 連結配線部

- 18 コンタクトパッド部

- り 19 エンドキャップ部

- 20 ゲート部を覆う遮光パターン部

- 21 レジスト

- 22 半導体シリコン基板

- 23 ゲート酸化膜

- 24 ポリシリコン膜

- 25 潜像領域

- 26 露光光

- 27 レベンソンマスク

- 28 トリムマスク

- 29 レジストパターン

- 30 コンタクト

- 33 第0領域

- 34 第1領域

- 35 第2領域

- 36 第3領域

- 37 第4領域

- 38 第5領域

- 39 第6領域

- 40 第7領域

- 41 近接する線分

- 42 抽出した図形の角のポイント

⋯【図6】

- 44 解像線幅

- 45 距離

·【図4】

18

·【図17】

| 第口框         | 200  | 220  | 275  | 330  | 385  | 440  | 550 |

|-------------|------|------|------|------|------|------|-----|

| [nm]        | ~220 | ~275 | ~330 | ~385 | ~440 | ~550 | ~   |

| 補正量<br>[nm] | -10  | (基準) | +10  | +20  | +25  | +30  | +25 |

·【図25】

·【図18】

| MD45        | 200  | 220  | 275  | 930  | 985  | 440  | 550 |

|-------------|------|------|------|------|------|------|-----|

| [nm]        | ~220 | ~275 | ~930 | ~385 | ~440 | ~550 | ~   |

| 特正量<br>[nm] | +10  | +10  | +5   | 0    | -5   | -10  | -10 |

## (19) 日本国特許庁 (JP)

# (12) 公開特許公報(A)

(11)特許出願公開番号 特開2001-83689 (P2001-83689A)

(43)公開日 平成13年3月30日(2001.3.30)

| (51) Int.Cl. <sup>7</sup> |        | 識別記号 | F I     |       | 7    | -7J-ト*(参考) |

|---------------------------|--------|------|---------|-------|------|------------|

| G03F                      | 1/08   |      | G 0 3 F | 1/08  | T    | 2H095      |

| G06F                      | 17/50  |      | G 0 6 F | 15/60 | 658M | 5B046      |

| H01L                      | 21/027 |      | H01L    | 21/30 | 502W |            |

## 審査請求 未請求 請求項の数6 OL (全 26 頁)

|                       | 12                      | A THE STATE OF THE |

|-----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 特願平11-260270          | (71)出顧人                 | 000003078                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       |                         | 株式会社東芝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 平成11年9月14日(1999.9.14) |                         | 神奈川県川崎市幸区堀川町72番地                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       | (72)発明者                 | 吉川 圭                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                       |                         | 神奈川県横浜市磯子区新杉田町8番地 株                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       |                         | 式会社東芝横浜事業所内                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                       | (72)発明者                 | 白井 聡                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                       | (                       | 神奈川県横浜市磯子区新杉田町8番地 株                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       |                         | 式会社東芝横浜事業所内                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                       | (74) <del>(128)</del> Å |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       | (14)142)(               | 弁理士 鈴江 武彦 (外6名)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       |                         | 开在工 即任 风多 (710年)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       |                         | 最終頁に続く                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                       |                         | 特願平11-260270 (71)出願人<br>平成11年9月14日(1999.9.14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## (54) 【発明の名称】 半導体製造用マスクのパターン補正方法およびそのパターン補正方法を記録した記録媒体

## (57) 【要約】

- ·【課題】十分な補正精度を得ることができる半導体製造 用マスクのパターン補正方法を提供すること。

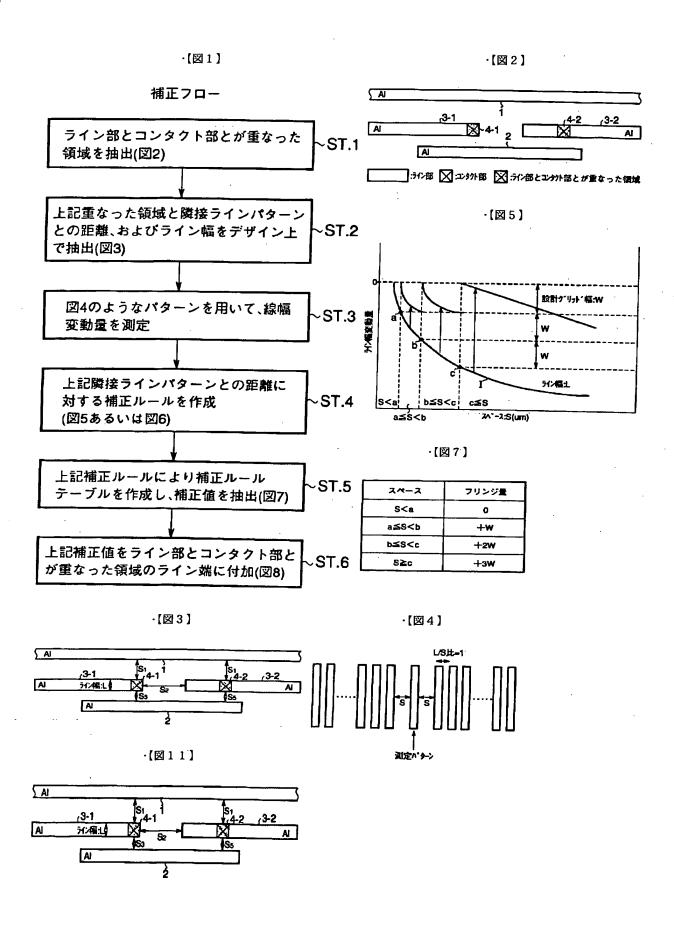

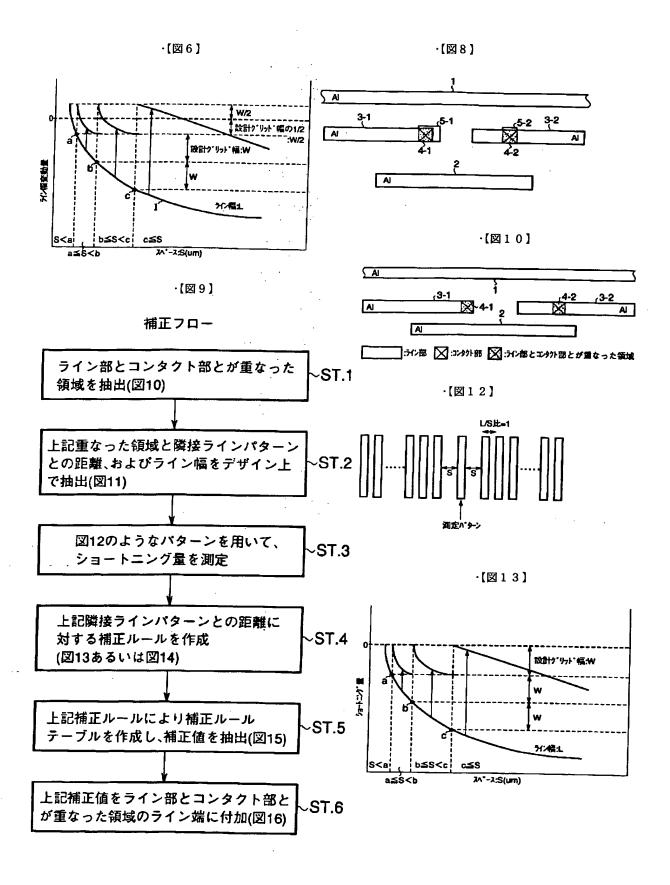

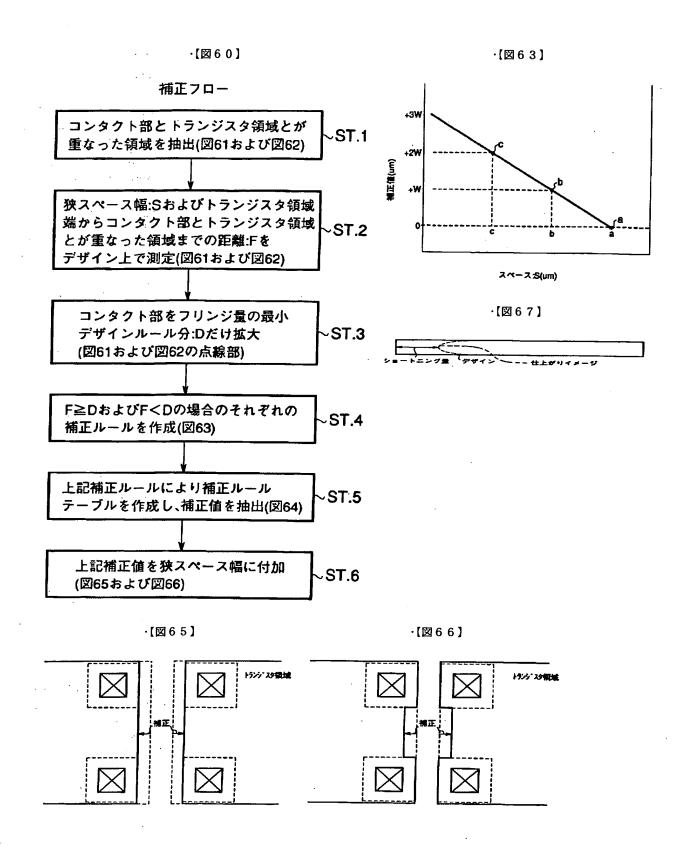

- ・【解決手段】ライン部とコンタクト部とが重なった領域を抽出し(ST. 1)、上記重なった領域とこの重なった領域に隣接する他のライン部とのスペース、および前記ライシ部のライン幅を抽出し(ST. 2)、ウェーハプロセス後に生ずるライン部のライン幅変動量とスペースとの依存性を取得し(ST. 3)、依存性を設計グリッド幅毎に分割し、この設計グリッド幅と依存性との交点を抽出し(ST. 4)、関係を交点区間毎に区切り、交点区間毎に、設計グリッド幅の整数倍の補正を行う補正ルールテーブルを作成し(ST. 5)、上記重なった領域に対し、補正ルールテーブルに基いた設計グリッド幅の整数倍の補正を行う(ST. 6)。

## ・【特許請求の範囲】

・【請求項1】 ライン部とコンタクト部とが重なった領 域を抽出する第1の工程と、

前記重なった領域とこの重なった領域に隣接する他のラ イン部とのスペース、および前記ライン部のライン幅を 抽出する第2の工程と、

前記ライン幅毎に、ウェーハプロセス後に生ずる前記ラ イン部のライン幅変動量と前記スペースとの関係を取得 する第3の工程と、

前記関係を設計グリッド幅毎に分割し、この設計グリッ ド幅と前記関係との交点を抽出する第4の工程と、

前記関係を交点区間毎に区切り、前記交点区間毎に、前 記設計グリッド幅の整数倍の補正を行う補正ルールテー ブルを作成する第5の工程と、

前記スペースと前記交点区間との対応関係を求め、前記 補正ルールテーブルに基いた前記設計グリッド幅の整数 倍の補正を、前記重なった領域に対して行う第6の工程 とを具備することを特徴とする半導体製造用マスクのパ ターン補正方法。

・【請求項2】 ライン部とコンタクト部とが重なった領 20 域を抽出する第1の工程と、

前記重なった領域とこの重なった領域に隣接する他のラ イン部とのスペース、および前記ライン部のライン幅を 抽出する第2の工程と、

前記ライン幅毎に、ウェーハプロセス後に生ずる前記ラ イン部のショートニング量と前記スペースとの関係を取 得する第3の工程と、

前記関係を設計グリッド幅毎に分割し、この設計グリッ ド幅と前記関係との交点を抽出する第4の工程と、

前記関係を交点区間毎に区切り、前記交点区間毎に、前 30 記設計グリッド幅の整数倍の補正を行う補正ルールテー ブルを作成する第5の工程と、

前記スペースと前記交点区間との対応関係を求め、前記 補正ルールテーブルに基いた前記設計グリッド幅の整数 倍の補正を、前記重なった領域に対して行う第6の工程 とを具備することを特徴とする半導体製造用マスクのパ ターン補正方法。

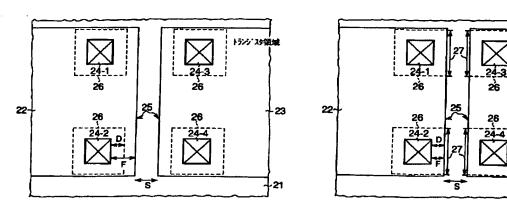

・【請求項3】 コンタクト部とトランジスタ領域とが重 なった領域を抽出する第1の工程と、

前記トランジスタ領域に隣接する他のトランジスタ領域 40 との間のスペース、および前記トランジスタ領域端から 前記重なった領域までの距離Fを抽出する第2の工程 ٤.

前記コンタクト部をデザインルールで規定された最小フ リンジ量D拡大する第3の工程と、

前記補正量とスペースとの関係を取得する第4の工程

前記関係を設計グリッド幅毎に分割し、この設計グリッ ド幅と前記関係との交点を抽出する第5の工程と、

記設計グリッド幅の整数倍の補正を行う補正ルールテー ブルを作成する第6の工程と、

前記スペースと前記交点区間との対応関係を求め、前記 補正ルールテーブルに基いた前記設計グリッド幅の整数 倍の補正を、D≦Fの場合、前記トランジスタ領域端の 全体に対して行い、F<Dの場合、前記トランジスタ領 域端の、前記トランジスタ領域端と前記拡大したコンタ クト部とが接する辺を除いた部分に対して行う第7のエ 程とを具備することを特徴とする半導体製造用マスクの 10 パターン補正方法。

・【請求項4】 ライン部とコンタクト部とが重なった領 域を抽出する第1の手順と、

前記重なった領域とこの重なった領域に隣接する他のラ イン部とのスペース、および前記ライン部のライン幅を 抽出する第2の手順と、

前記ライン幅毎に、ウェーハプロセス後に生ずる前記ラ イン部のライン幅変動量と前記スペースとの関係を取得 する第3の手順と、

前記関係を設計グリッド幅毎に分割し、この設計グリッ ド幅と前記関係との交点を抽出する第4の手順と、

前記関係を交点区間毎に区切り、前記交点区間毎に、前 記設計グリッド幅の整数倍の補正を行う補正ルールテー ブルを作成する第5の手順と、

前記スペースと前記交点区間との対応関係を求め、前記 補正ルールテーブルに基いた前記設計グリッド幅の整数 倍の補正を、前記重なった領域に対して行う第6の手順 とを記録したことを特徴とするコンピュータにより読み 取り可能な記録媒体。

・【請求項5】 ライン部とコンタクト部とが重なった領 域を抽出する第1の手順と、

前記重なった領域とこの重なった領域に隣接する他のラ イン部とのスペース、および前記ライン部のライン幅を 抽出する第2の手順と、

前記ライン幅毎に、ウェーハプロセス後に生ずる前記ラ イン部のショートニング量と前記スペースとの関係を取 得する第3の手順と、

前記関係を設計グリッド幅毎に分割し、この設計グリッ ド幅と前記関係との交点を抽出する第4の手順と、

前記関係を交点区間毎に区切り、前記交点区間毎に、前 記設計グリッド幅の整数倍の補正を行う補正ルールテー ブルを作成する第5の手順と、

前記スペースと前記交点区間との対応関係を求め、前記 補正ルールテーブルに基いた前記設計グリッド幅の整数 倍の補正を、前記重なった領域に対して行う第6の手順 とを記録したことを特徴とするコンピュータにより読み 取り可能な記録媒体。

・【請求項6】 コンタクト部とトランジスタ領域とが重 なった領域を抽出する第1の手順と、

前記トランジスタ領域に隣接する他のトランジスタ領域 前記関係を交点区間毎に区切り、前記交点区間毎に、前 50 との間のスペース、および前記トランジスタ領域端から

3

前記重なった領域までの距離Fを抽出する第2の手順 レ

前記コンタクト部をデザインルールで規定された最小フリンジ量D拡大する第3の手順と、

前記補正量とスペースとの関係を取得する第4の手順 と、

前記関係を設計グリッド幅毎に分割し、この設計グリッド幅と前記関係との交点を抽出する第5の手順と、 前記関係を交点区間毎に区切り、前記交点区間毎に、前 記設計グリッド幅の整数倍の補正を行う補正ルールテー ブルを作成する第6の手順と、

前記スペースと前記交点区間との対応関係を求め、前記補正ルールテーブルに基いた前記設計グリッド幅の整数倍の補正を、D≦Fの場合、前記トランジスタ領域端の全体に対して行い、F<Dの場合、前記トランジスタ領域端の、前記トランジスタ領域端と前記拡大したコンタクト部とが接する辺を除いた部分に対して行う第7の手順とを記録したことを特徴とするコンピュータにより読み取り可能な記録媒体。

- ・【発明の詳細な説明】

- $\cdot [0001]$

·【発明の属する技術分野】この発明は、半導体装置製造におけるリソグラフィ工程で用いられる露光用マスクのパターン補正方法とマスクパターン補正装置、そしてそれらを用いた露光用マスクと半導体装置に関する。

.[0002]

・【従来の技術】近年、半導体デバイスの微細化に伴い、 仕上がりが設計寸法通りにできない箇所の問題が顕在化 してきた。その一例として、ライン終端部のショートニ シグが挙げられる。ショートニングの原因としては、マ 30 スクが設計寸法通りにできていない、ライン終端のコー ナー部がすでに光の解像限界である、また、エッチング による変換差などが挙げられる。

・【0003】ボーダーレスコンタクトの配線パターンを 例にとると、コンタクトの落ちるライン終端がショート ニングした場合、ラインとコンタクトホールとの接触面 積が減少し、ヴィア抵抗の上昇を引き起こす。これは、 デバイスのパフォーマンスを落とす一因となる。

・【0004】このようなショートニングを回避するため、コンタクト部に対して予め、ある程度のフリンジ量 40 を付けて設計する、あるいは実験により見積もったフリンジ量を補正ツールを使うことにより一律に付ける手法が一般的に用いられている。

·【0005】しかし、ショートニング量等の仕上がり誤 差は、パターンの疎密、あるいは線幅などにより変化す ることが十分に考えられる。

$\cdot [00006]$

・【発明が解決しようとする課題】このように、従来のマスクパターン補正方法では、仕上がり誤差のパターン依存性が考慮されておらず、十分な補正精度が必ずしも得 50

4

られてはいない、という事情がある。

·【0007】この発明は、上記事情に鑑み為されたもので、その目的は、十分な補正精度を得ることができる半導体製造用マスクのパターン補正方法を提供することにある。

$\{8000\}$

・【課題を解決するための手段】上記目的を達成するために、この発明の第1の態様に係る半導体製造用マスクのパターン補正方法は、ライン部とコンタクト部とが重なった領域を抽出し、前記重なった領域とこの重なった領域を抽出し、前記重なった領域とこの重なった領域に隣接する他のライン部とのスペース、および前記ライン部のライン幅を抽出し、前記ライン幅毎に、ウェーハプロセス後に生ずる前記のヨインに要いて、前記関係を取得し、前記関係を設計グリッド幅を設計グリッド幅の整数倍の補正を行う補正ルールテーブルを作成し、前記スペースと前記で点区間毎に、前記設計グリッド幅の整数倍の補正を行う補正ルールテーブルを作成し、前記スペースと前記で点区間との対応関係を求め、前記補正ルールテーブルに基いた前記設計グリッド幅の整数倍の補正を、前記重なった領域に対して行うことを特徴としている。

【0009】また、上記目的を達成するために、この発明の第2の態様に係る半導体製造用マスクのパターン補正方法は、ライン部とコンタクト部とが重なった領域を抽出し、前記重なった領域とこの重なった領域に隣接する他のライン部とのスペース、および前記ライン部のライン幅を抽出し、前記ライン幅毎に、ウェーハプロスへ後に生ずる前記ライン部のショートニング量と前記スペースとの関係を取得し、前記関係を設計グリッド幅と前記関係との交点を間毎に、前記関係を交点区間毎に区切り、前記交点区間毎に、前記設計グリッド幅の整数倍の補正を行う補正ルールテーブルを作成し、前記スペースと前記交点区間に、前記設計グリッド幅の整数倍の補正を行う補正ルの対応関係を求め、前記和エルー・ブルに基いた前記設計グリッド幅の整数倍の補正を、前記重なった領域に対して行うことを特徴としている。

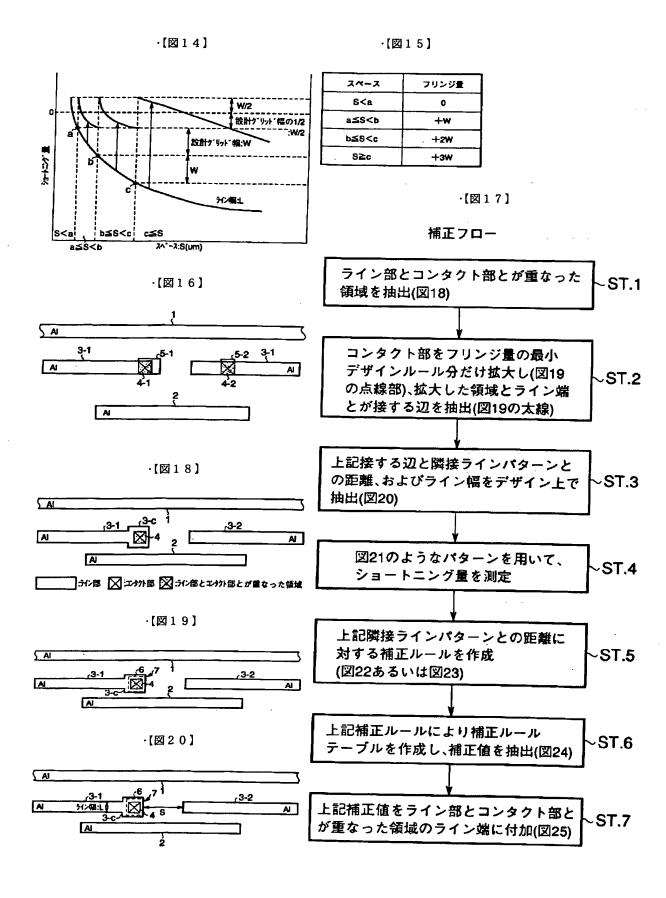

・【0010】また、上記目的を達成するために、この発明の第3の態様に係る半導体製造用マスクのパターン補正方法は、ライン部とコンタクト部とが重なった領域を抽出し、前記コンタクト部をデザインルールで規定された最小フリンジ量拡大し、拡大したコンタクト部と前記重なった領域に隣接する辺を抽出し、前記重なった領域とこの重なった領域に隣接する他のライン部とのスペース、および前記ライン部のライン幅を抽出し、前記の設備を設計グリッド幅毎に、ウェーハプロセス後に生ずる前記ラインのショートニング量と前記スペースとの関係を取得し、前記関係を設計グリッド幅毎に分割し、この設計グリッド幅と前記関係との交点を抽出し、前記関係を交点区間毎に区切り、前記交点区間毎に、前記設計グリッド幅の整数倍の補正を行う補正ルールテーブルを作成し、前記ス

ペースと前記交点区間との対応関係を求め、前記補正ルールテーブルに基いた前記設計グリッド幅の整数倍の補正を、前記接する辺に対して行うことを特徴としている。

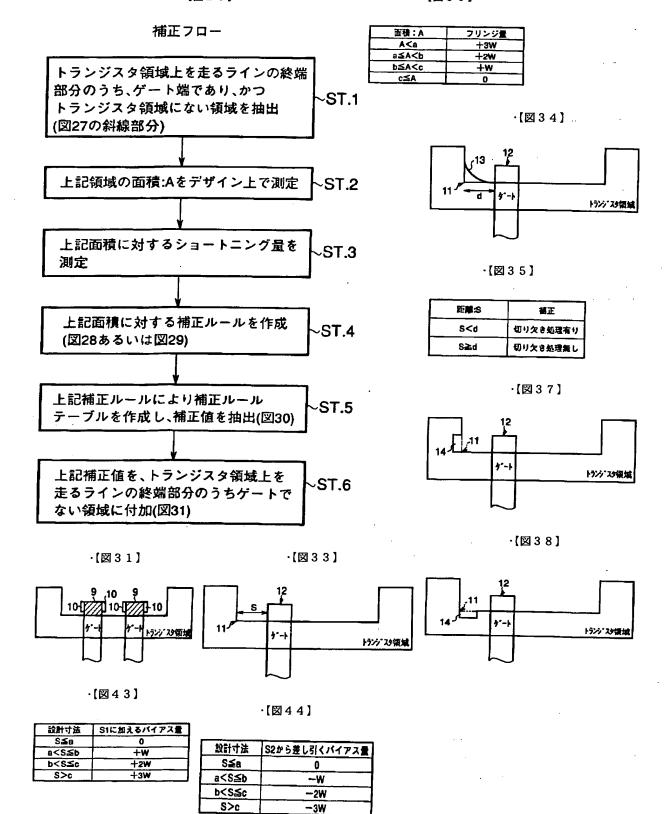

・【0011】また、上記目的を達成するために、この発 明の第4の態様に係る半導体製造用マスクのパターン補 正方法は、トランジスタ領域上を走るライン部の終端部 分のうち、ゲート端であり、かつトランジスタ領域上に ない領域を抽出し、前記ゲート端であり、かつトランジ スタ領域上にない領域の面積を抽出し、前記面積毎に、 ウェーハプロセス後に生ずる前記ライン部のショートニ シグ量と前記面積との関係を取得し、前記関係を設計グ リッド幅毎に分割し、この設計グリッド幅と前記関係と の交点を抽出し、前記関係を交点区間毎に区切り、前記 交点区間毎に、前記設計グリッド幅の整数倍の補正を行 う補正ルールテーブルを作成し、前記スペースと前記交 点区間との対応関係を求め、前記補正ルールテーブルに 基いた前記設計グリッド幅の整数倍の補正を、前記ゲー ト端であり、かつトランジスタ領域上にない領域に対し て行うことを特徴としている。

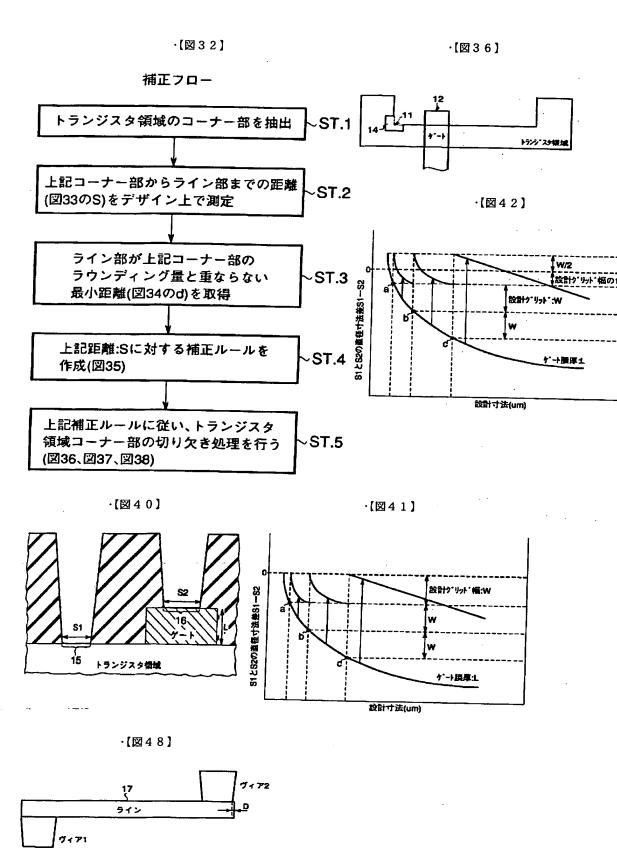

・【0012】また、上記目的を達成するために、この発明の第5の態様に係る半導体製造用マスクのパターン補正方法は、トランジスタ領域のコーナー部を抽出し、前記コーナー部からライン部までの距離を抽出し、前記ライン部が前記コーナー部のラウンディングと重ならない最小距離を取得し、前記ライン部が前記コーナー部のラウンディングと重なる場合、切り欠き処理を、前記コーナー部に対して行うことを特徴としている。

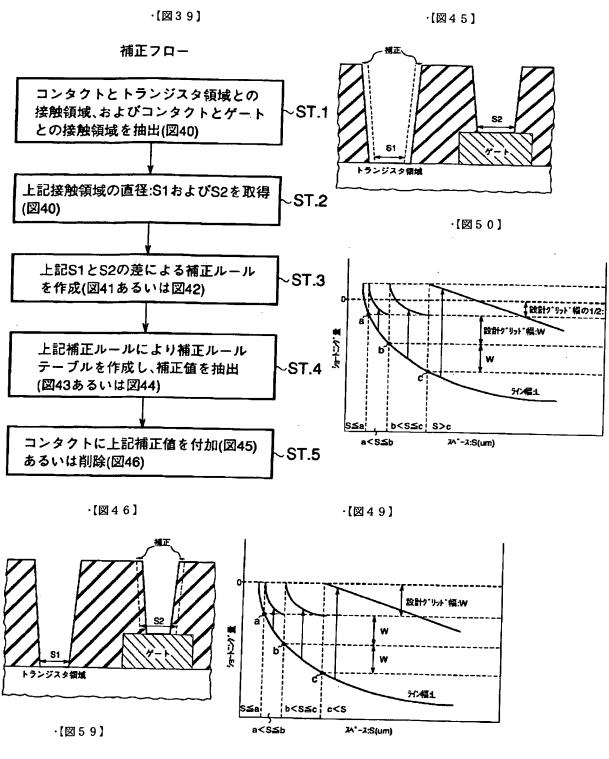

・【0013】また、上記目的を達成するために、この発明の第6の態様に係る半導体製造用マスクのパターン補近方法は、コンタクト部がトランジスタ領域に接触する第1の接触領域、およびコンタクト部がライン部に接触する第2の接触領域を抽出し、前記第1、第2の接触領域の直径を抽出し、前記第1、第2の接触領域の直径差と、前記ライン部の寸法との関係を取得し、前記関係を設計グリッド幅毎に分割し、この設計グリッド幅と前記関係との交点を抽出し、前記関係を交点区間毎に区切り、前記交点区間毎に、前記設計グリッド幅の整数倍の補正を行う補正ルールテーブルを作成し、前記ライン部の寸法と前記交点区間との対応関係を求め、前記補正ルールテーブルに基いた前記設計グリッド幅の整数倍の補正を、前記前記第1の接触領域および前記第2の接触領域のいずれかに対して行うことを特徴としている。

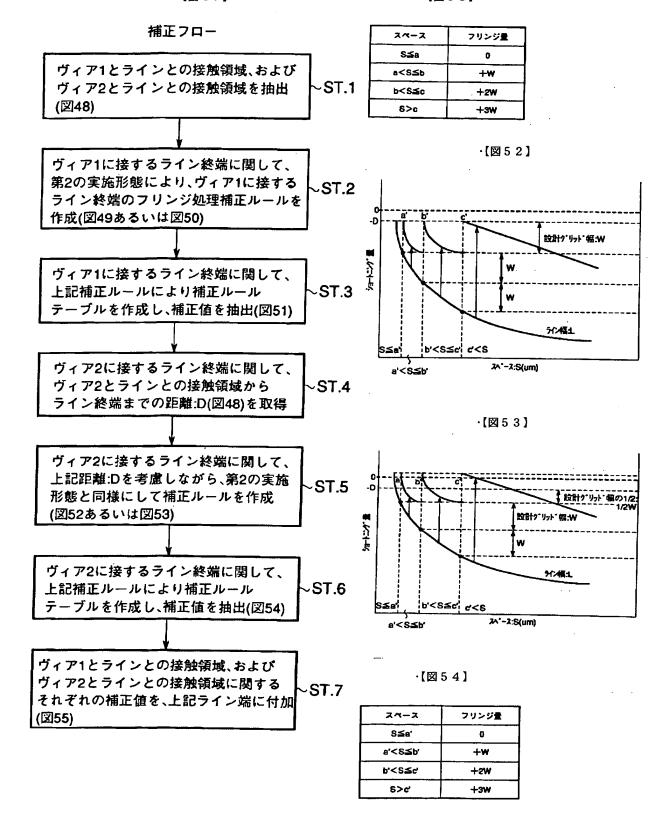

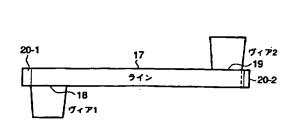

・【0014】また、上記目的を達成するために、この発明の第7の態様に係る半導体製造用マスクのパターン補正方法は、コンタクト部に対してライン部が重なる第1の領域、およびライン部に対してコンタクト部が重なる第2の領域を抽出し、前記第1の領域とこの第1の領域に隣接する他のライン部とのスペース、および前記ライシ部のライン幅を抽出し、前記ライン幅毎に、ウェーハ 50

6

プロセス後に生ずる前記ライン部のショートニング量と 前記スペースとの第1の関係を取得し、前記関係を設計 グリッド幅毎に分割し、この設計グリッド幅と前記関係 との交点を抽出し、前記関係を交点区間毎に区切り、前 記交点区間毎に、前記設計グリッド幅の整数倍の補正を 行う補正ルールテーブルを作成し、前記第2の領域から 前記ライン部の終端までの距離を抽出し、前記ライン幅 毎に、ウェーハプロセス後に生ずる前記ライン部のショ ートニング量と前記第2の領域から前記ライン部の終端 までの距離との第2の関係を取得し、前記関係を設計グ リッド幅毎に分割し、この設計グリッド幅と前記関係と の交点を抽出し、前記関係を交点区間毎に区切り、前記 交点区間毎に、前記設計グリッド幅の整数倍の補正を行 う補正ルールテーブルを作成し、前記スペースと前記交 点区間との対応関係、および前記第2の領域から前記ラ イン部の終端までの距離との対応関係を求め、前記補正 ルールテーブルに基いた前記設計グリッド幅の整数倍の 補正を、前記第1、第2の領域に対して行うことを特徴 としている。

・【0015】また、上記目的を達成するために、この発 明の第8の態様に係る半導体製造用マスクのパターン補 正方法は、コンタクト部とトランジスタ領域とが重なっ た領域を抽出し、前記トランジスタ領域に隣接する他の トランジスタ領域との間のスペース、および前記トラン ジスタ領域端から前記重なった領域までの距離Fを抽出 し、前記コンタクト部をデザインルールで規定された最 小フリンジ量D拡大し、前記補正量とスペースとの関係 を取得し、前記関係を設計グリッド幅毎に分割し、この 設計グリッド幅と前記関係との交点を抽出し、前記関係 を交点区間毎に区切り、前記交点区間毎に、前記設計グ リッド幅の整数倍の補正を行う補正ルールテーブルを作 成し、前記スペースと前記交点区間との対応関係を求 め、前記補正ルールテーブルに基いた前記設計グリッド 幅の整数倍の補正を、D≦Fの場合、前配トランジスタ 領域端の全体に対して行い、F<Dの場合、前記トラン ジスタ領域端の、前記トランジスタ領域端と前記拡大し たコンタクト部とが接する辺を除いた部分に対して行う ことを特徴としている。

·【0016】上記構成を有する半導体製造用マスクのパターン補正方法であると、

(1) ウェーハプロセス後に生ずるライン部のライン幅変動量と、ライン部とコンタクト部とが重なった領域とこの重なった領域に隣接する他のライン部とのスペースとの関係。

・【0017】(2)ウェーハプロセス後に生ずるライン部のショートニング量と、ライン部とコンタクト部とが重なった領域とこの重なった領域に隣接する他のライン部とのスペースとの関係。

·【0018】(3)ウェーハプロセス後に生ずるライン 部のショートニング量とトランジスタ領域上を走るライ シ部の終端部分のうち、ゲート端であり、かつトランジ スタ領域上にない領域の面積との関係。

・【0019】(4)ウェーハプロセス後に生ずるトランジスタ領域のラウンディング量とライン部との関係。・【0020】(5)ウェーハプロセス後に生ずるコンタクト部がトランジスタ領域に接触する第1の接触領域、およびコンタクト部がライン部に接触する第2の接触領域の直径差と、ライン部の寸法との関係。

・【0021】(6)ウェーハプロセス後に生ずるライン部のショートニング量とライン部に対してコンタクト部が重なる領域からライン部の終端までの距離との関係。・【0022】(7)補正量と一のトランジスタ領域に隣接する他のトランジスタ領域との間のスペースとの関係、拡大したコンタクト部が一のトランジスタ領域に接するか否か。

·【0023】上記(1)~(7)のように、補正するパターンの周囲の環境を考慮するので、周囲の環境を考慮しない補正方法に比べて、十分な補正精度を得ることができる。

## $\cdot [0024]$

·【発明の実施の形態】以下、この発明の実施形態を図面を参照して説明する。この説明に際し、全図にわたり、 共通する部分には共通する参照符号を付す。

・【0025】 [第1の実施形態] まず、この発明の第1の実施形態に係るマスクパターン補正方法を説明する。・【0026】第1の実施形態は、ボーダーレスコンタクトを有する配線パターン(ライン部)において、コンタクト部と重なった領域のパターンを、その領域周囲のパターンの疎密、およびライン部のライン幅を考慮して補正し、変更するフリンジ処理である。

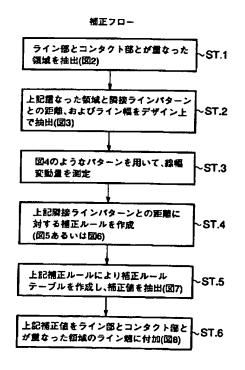

・【0027】図1は、第1の実施形態に係るマスクパターン補正方法を示す流れ図、図2~図8はそれぞれ、図1に示す各ステップを説明するための図である。

・【0028】図1に示すステップST.1において、まず、ライン部とコンタクト部とが重なった領域を抽出する。図2に、第1の実施形態に用いられた、ライン部、コンタクト部、およびこれらが重なった領域をそれぞれ持つパターンの一例を示す。なお、図2に示す一例は、デザイン上、たとえばCADデータ上のものである。・【0029】図2に示すように、一例に係るパターンは、互いに並行するライン部1、2、3-1、3-2をそれぞれ持つ。ライン部3-1、3-2はそれぞれ、ライン部1とライン部2との間に配置されている。コンタクト部4-1は、ライン部3-1の終端に重なっている。また、コンタクト部4-2は、ライン部3-2の中程に重なり、その終端には重なっていない。

·【0030】次に、ステップST. 2において、上記重なった領域と、これに隣接するライン部とのスペース・(距離) をそれぞれ、デザイン上、たとえばCADデータ上で抽出する。

R

【0031】ここで、上記スペースに関しては、図3に示すように、ライン部の終端に重なるコンタクト部4-1の場合、重なった領域の三辺それぞれに相対したライン部までのスペースをそれぞれ抽出する。一方、コンタクト部4-2のように、ライン部の中程のみに重なる場合には、重なった領域の二辺それぞれに相対したライン部までのスペースをそれぞれ抽出する。

・【0032】上記一例に係るパターンにおいては、コンタクト部4-1からライン部1までのスペースS<sub>1</sub>: コンタクト部4-1からライン部3-2までのスペースS<sub>2</sub>: およびコンタクト部4-1からライン部2までのスペースS<sub>3</sub>をそれぞれデザイン上で測定し、抽出した。また、コンタクト部4-2からライン部1までのスペースS<sub>4</sub>: およびコンタクト部4-2からライン部3-2までのスペースS<sub>5</sub>をそれぞれデザイン上で測定し、抽出した。

$\cdot$ 【0033】さらにステップST. 2において、スペースS<sub>1</sub> $\sim$ S<sub>5</sub>の他、ライン部のライン幅を抽出する。

・【0034】上記一例に係るパターンにおいては、コンタクト部4-1が重なるライン部3-1のライン幅Lをデザイン上で測定し、抽出した。なお、ライン部3-1のライシ幅Lと、ライン幅3-2のライン幅とは互いに等しい。・【0035】次に、ステップST.3において、スペースとライン幅変動量との関係を、実験的、あるいはションにより取得する。この関係は、実験的に取得する場合、図4に示すようなライン・アンド・スへハース(L/S)パターンを持つ測定パターンをウェース(L/S)パターンを持つ測定パターンをウェースに形成し、これを走査型電子顕微鏡(SEM)や電気的測定を用いて、ライン幅変動量を測定すれば良い。また、シミュレーションにより取得する場合には、図4に示すような測定パターンを製造プロセスシミュレータに再現させ、そのライン幅変動量を計算すれば良い。

・【0036】次に、ステップST.4において、取得したスペースとライン幅変動量との関係を用いて、隣接するライン部とのスペースに対する補正ルールを作成する。スペースとライン幅変動量との関係を、図5および図6に示す。

【0037】図5および図6に示すように、一例に係るパターンにおいては、ライン幅Lは、スペースSが大きくなる程、ライン幅変動量が"0"、即ち設計値から大きくずれる(変動極性I)。つまり、スペースSが大きくなる程、ライン幅Lは細くなる。このような傾向に基き、第1の実施形態では、上記重なった領域に対して、スペースSが大きくなるにしたがって、上記重なった領域の幅が大きくなるようにパターンを補正する補正ルールを作成する。

・【0038】次に、ステップST. 5において、上記補 正ルールにより、補正ルールテーブルを作成する。この ために、図5および図6に示すように、縦軸(ライン幅 変動量)を、設計グリッド幅W毎に分割する(設計グリ ッド幅Wは、たとえばCAD上で一度に付加することの できる最小の幅である。)。次に、設計グリッド幅Wと変動曲線 I との交点をそれぞれ抽出する。この作業によって得た交点をそれぞれ "a"、"b"、"c"とする。次に、スペースSが"S < a"の範囲では、補正値を"0"とし、スペースSが"a  $\le$  S < b"の範囲では、"+W"の補正値を設ける。さらにスペースSが"b  $\le$  S < c"の範囲では、"+2W"の補正値を設け、スペースSが"c  $\le$  S"の範囲では、"+3W"の補正値を設ける。このような作業により、図7に示すような補正ルールテーブルが作成される。

·【0039】さらにステップST.5において、作成した補正ルールテーブルから、ステップST.2で求めたスペースS1、S2、S3、S4、S5に対する補正値を抽出する。

・【0040】次に、ステップST.6において、抽出した補正値を、ライン部とコンタクト部とが重なった領域のライン端に、フリンジ量として付加する。このフリンジ処理は、この発明に適合した補正ツールをプログラムにより作成し、たとえばCADに格納しておき、適宜用いることで、自動的に行うことができる。フリンジ処理 20が終了した状態の一例に係るパターンを、図8に示す。図8に示すように、上記重なった領域にはそれぞれ、フリンジ5-1、5-2が設けられている。

・【0041】このような第1の実施形態によれば、ライシ部とコンタクト部とが重なった領域に対して、パターシの疎密、およびそのライン幅等、その周囲の環境を考慮した補正フリンジ量を求め、求めた補正フリンジ量を、補正ルールテーブル化しておく。この後、補正ルールテーブルに従って、補正ツールを用いて自動でフリンジ処理を行う。

·【0042】このようなフリンジ処理が行われた半導体製造用マスクを用いて、ウェーハプロセスにより形成されたパターンにおいては、たとえば周囲の環境に関係なく一律なフリンジ処理を行ったマスクを用いた場合に比べて、上記重なった領域を、より設計値に近い状態、あるいは設計値通りに仕上げることができる。

·【0043】このように上記重なった領域が、より設計値に近い状態に仕上がることで、たとえばコンタクト面積の減少等に伴ったコンタクト抵抗の上昇の問題等を、回避できる。よって、形成された集積回路においては、設計値に近いコンタクト抵抗を得ることができ、回路上、期待される電気的パフォーマンスを、容易に得ることができる。

・【0044】また、補正ルールの一例(図5)と、他の例(図6)との違いは、ライン幅変動量"0"を基準にして補正値を"W"ずつ付けていくか、ライン幅変動量・"0"に設計グリッド幅Wの1/2を足した値を基準にして補正値を"W"ずつ付けていくかである。どちらの例でも、ウェーハ上に形成されたパターンを、設計値に近い状態、あるいは設計値通りに仕上げることができ

10

る。

【0045】しかし、図6に示す設計グリッド幅Wの1 ×2を足した値を基準にして補正値を"+W"ずつ付け ていく他の例のほうが、設計値に近い状態、あるいは設 計値通りに仕上がり易い。

・【0046】なぜならば図5に示す一例においては、たとえば "S < c"のとき、ライン幅Lの変動を、ライン幅変動量 "0" (即ち設計値)から "-W"の範囲に変動に抑えることができるのに対し、図6に示す他の例においては、ライン幅変動量 "0" (即ち設計値)から・"±W/2"の範囲に、さらに変動を抑えることができるからである。

【0047】また、図8に示すように、上記一例に係るパターンにおいては、ライン幅Lを持つライン部3-1、3-2に対してフリンジ5-1、5-2を付加する補正を行ったが、ライン幅上以外のライン幅が存在する場合には、各ライン幅毎にそれぞれ、上記と同様な方法で補正ルールを作成し、この補正ルールにより補正ルールテーブルを作成する。この後、ライン幅毎に、それぞれ作成した補正ルールテーブルに基いてフリンジを付加する補正を行えば良い。

・【0048】 [第2の実施形態] 次に、この発明の第2の実施形態に係るマスクパターン補正方法を説明する。・【0049】第2の実施形態は、第1の実施形態と同様に、ボーダーレスコンタクトを有する配線パターン(ライン部)において、コンタクト部と重なった領域のパターンを、その領域周囲のパターンの疎密、およびライン部のライン幅を考慮して補正し、変更するフリンジ処理である。異なるところは、第1の実施形態では、ライン部のショートニング量とスペースとの関係に基づき、補正ルールを作成するようにしたことである。

・【0050】図9は、第2の実施形態に係るマスクバターン補正方法を示す流れ図、図10~図16はそれぞれ、図9に示す各ステップを説明するための図である。・【0051】まず、図9に示すステップST.1において、ライン部とコンタクト部とが重なった領域を抽出する。図10に、第2の実施形態に用いられた、パターンの一例を示す。なお、図10に示す一例は、デザイン上、たとえばCADデータ上のものであり、図2に示した一例と同様のパターンである。

・【0052】次に、ステップST. 2において、上記重なった領域と、これに隣接するライン部とのスペース・(距離)をそれぞれ、デザイン上、たとえばCADデータ上で抽出する。

・【0053】 ここで、上記スペースに関しては、第1の 実施形態と同様に、コンタクト部4-1からライン部1までのスペースS<sub>1</sub>: コンタクト部4-1からライン部3-2 までのスペースS<sub>2</sub>: コンタクト部4-1からライン部2